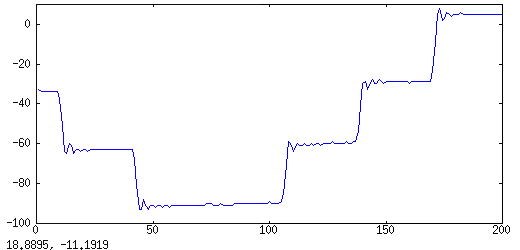

For this test, the A/D feeds samples to a NEXYS 2 FPGA board, and a small Octave program

uploads the data via the USB port and displays it. The test signal is an

8-level stepped waveform being generated by the VGA port of the NEXYS 2; the signal

is connected to the input of one channel through a 0.1 uF capacitor.

Samples are captured into RAM at the full 100MHz sampling rate; both the

the steps and and the ringing of the filters are clearly visible. The plot

shows a 200-sample section of the 2048-sample segment that was captured.

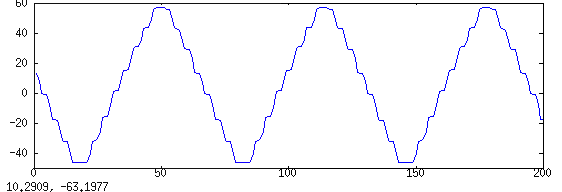

The next plot is the same signal. It's still sampled at 100MHz,

but this time the CIC lowpass filter desamples to 6.67MHz before storing

the samples in the FPGA's block RAM. Effects of the filter on the step

transitions are clearly visible.

|

|

Hosted by

|

Last updated

$Date: 2009/08/11 21:35:45 $ |